# 8 Enhanced USB single-chip CH552, CH551

#### Manual

#### Version: 1

#### http://wch.cn

#### 1 Overview

CH552 chip is a microcontroller core E8051 compatible MCS51 enhanced instruction set that 79% of single-byte instructions are single cycle instructions, instruction average velocity MCS51 8 to 15 times faster than the standard.

CH552 system supports up to 32MHz frequency, built 16K bytes of program memory ROM and 256 bytes of internal iRAM 1K and the inner sheet xRAM, xRAM supports direct memory access DMA.

CH552 built ADC analog to digital converter, a capacitance detection touch key, group 3 and the PWM signal acquisition and timers, dual asynchronous serial interface, SPI, USB full-speed device controller and transceiver function modules.

CH551 to CH552 is a simplified version, only program memory ROM 10K, the sheet xRAM only 512 bytes, only asynchronous serial UART0 provided, only SOP16 package, and removes the ADC analog to digital conversion module and a USB type-C module in addition addition to the above difference with the same CH552, CH552 direct reference manuals and information.

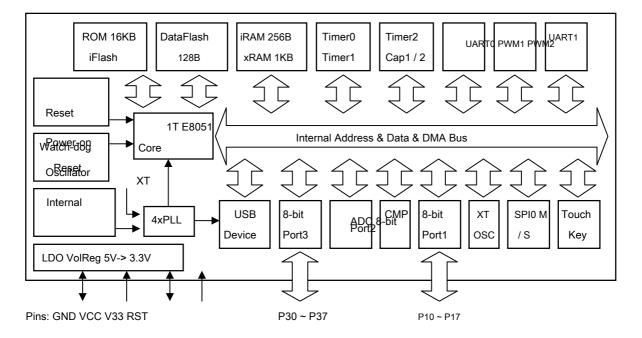

The following is an internal block diagram CH552 for reference purposes only.

## 2. Features

I Core: Enhanced E8051 core MCS51 compatible instruction set which 79% of single-byte instructions are single cycle instructions, instruction average

Faster than standard MCS51 8 ~ 15 times, specific data XRAM fast copy instruction, dual DPTR pointer.

I ROM: 16KB capacity reprogrammable non-volatile memory ROM, may all be used to program memory space; or may be divided

And a program storage area for the 2KB 14KB boot code BootLoader / ISP program area.

- I DataFlash: 128 bytes of data can be repeatedly rewritable nonvolatile memory, support rewriting data in bytes.

- I RAM: 256 bytes of internal iRAM, can be used for temporary storage and fast data stack; 1KB inner sheet xRAM, may be used in large amounts According to scratch and DMA Direct Memory Access.

I USB: Embedded USB transceiver and the USB controller support the USB-Device device mode, supports USB type-C master-slave detection,

Support USB 2.0 full-speed 12Mbps or low-speed 1.5Mbps. Supports up to 64-byte packets, the FIFO built, support DMA.

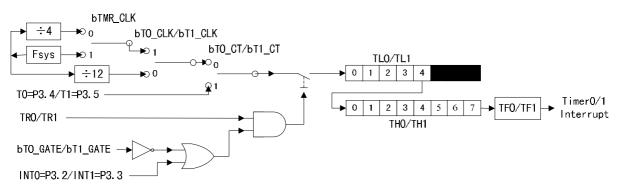

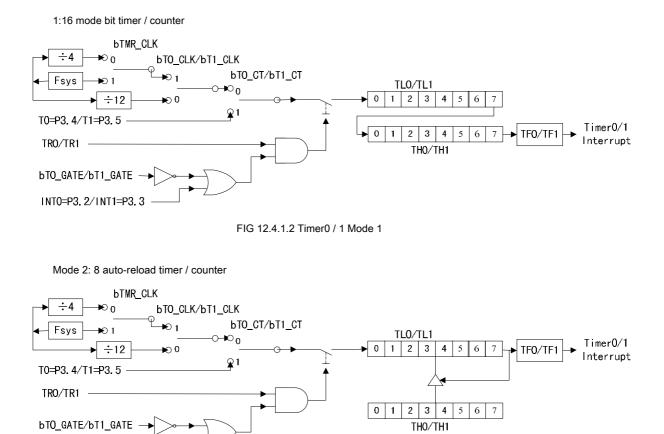

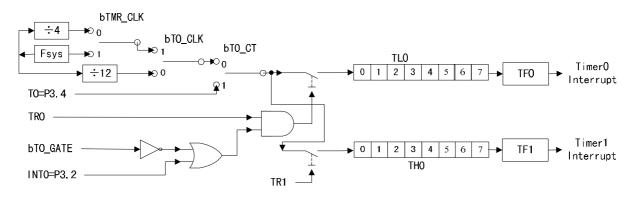

I Timer: 3 sets a timer, T0 / T1 / T2 standard MCS51 timer.

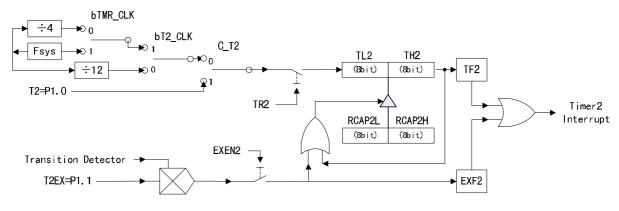

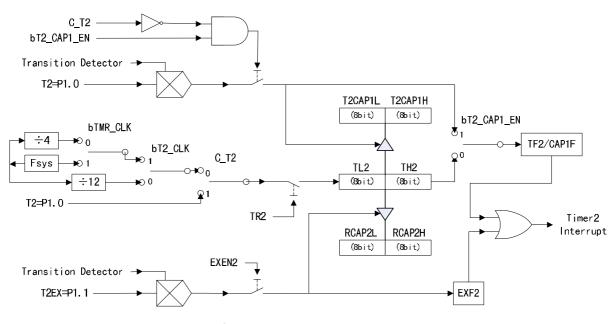

I Capture: Timer T2 extended to support 2-channel signal capture.

I PWM: PWM outputs 2, PWM1 / PWM2 2 8-bit PWM output.

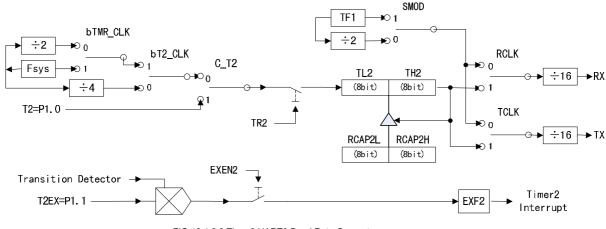

I UART: 2 groups of asynchronous serial ports, support higher baud rate, UART0 standard MCS51 serial port.

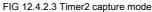

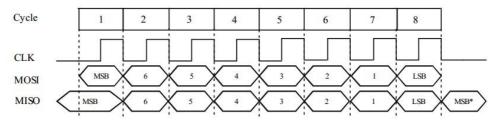

I SPI: SPI controller built-in the FIFO, up to half the clock frequency of the system frequency Fsys with serial data input and output

Simplex multiplexing, supports Master / Slave mode from the master.

I ADC: 4 channel 8-bit A / D analog-digital converter, a voltage comparator support.

I Touch-Key: 6-channel capacitive sensing, supports up to 15 touch keys, support independent timer interrupt.

I GPIO: GPIO pins support up to 17 (inclusive XI / XO and RST signal pins and USB).

I Interrupt: Support group interrupt signal source 14, including a standard group 6 MCS51 compatible interrupt (INT0, T0, INT1, T1,

UART0, T2), and an extended set of 8 interrupt (SPI0, TKEY, USB, ADC, UART1, PWMX, GPIO, WDOG), wherein the GPIO interrupts may be selected from seven pins.

I Watch-Dog: 8-bit watchdog timer preset WDOG, support the timer interrupt.

I Reset: reset signal supports four source, and internal power-on reset, reset and watchdog timeout support software reset, optional outer pin

Reset input unit.

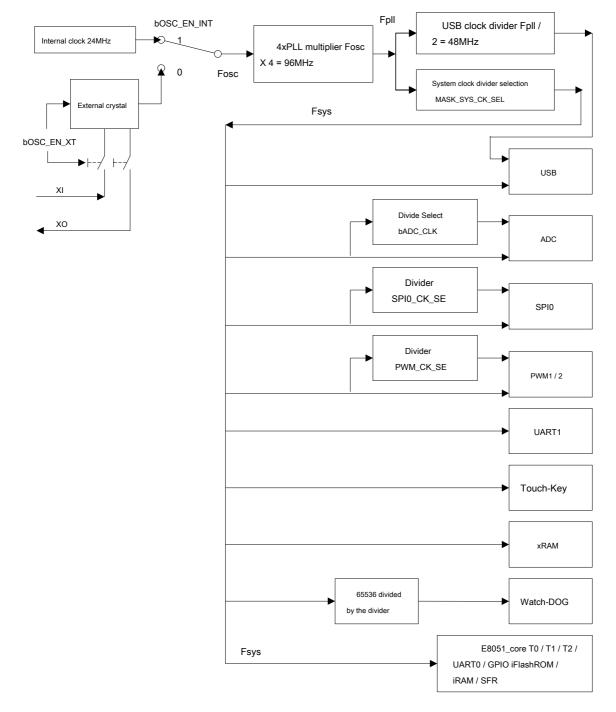

I Clock: Built 24MHz clock source, may be supported by multiplexing GPIO pin external crystal.

I Power: low-dropout voltage regulator 5V to 3.3V, 3.3V, or even support 2.8V 5V supply voltage. Support low power

Loss of sleep, support for USB, UART0, UART1, SPI0 as well as some external GPIO wake.

I Chip built a unique ID number.

### 3, the package

| CH552T       P3.2 / TXD1_/ INT0 / VBUS1 / AIN3 1       P1.4 / T2_ / CAP1_/ SCS / TIN2 / UCC1 / AIN1 2     VCC / VDD       P1.5 / MOSI / PWM1 / TIN3 / UCC2 / AIN2 3     GND / VSS       P1.6 / MISO / RXD1 / TIN4 4     P1.2 / XI / RXD_       P1.7 / SCK / TXD1 / TIN5 5     P1.3 / XO / TXD_       RST / T2EX_/ CAP2_6     P3.7 / UDM       P1.0 / T2 / CAP1 / TIN0 7     P3.6 / UDP       P1.1 / T2EX / CAP2 / TIN1 / VBUS2 / AIN0 8     P3.5 / T1       P3.1 / PWM2_/ TXD 9     P3.4 / PWM2 / RXD1_/ T0       P3.0 / PWM1_/ RXD 10     P3.3 / INT1 | 20<br>19<br>18<br>17<br>16<br>15<br>14<br>13<br>12<br>11 | CH552G<br>P3.2 / TXD1_/ INT0 / VBUS1 / AIN3 1<br>P1.4 / T2_/ CAP1_/ SCS / TIN2 / UCC1 / AIN1 2 VCC / VDD<br>P1.5 / MOSI / PWM1 / TIN3 / UCC2 / AIN2 3 GND / VSS<br>P1.6 / MISO / RXD1 / TIN4 4 P3.7 / UDM<br>P1.7 / SCK / TXD1 / TIN5 5 P3.6 / UDP<br>RST / T2EX_/ CAP2_6 P3.4 / PWM2 / RXD1_/ T0<br>P3.1 / PWM2_/ TXD 7 P3.3 / INT1<br>P3.0 / PWM1_/ RXD 8 P1.1 / T2EX / CAP2 / TIN1 / VBUS2 / AIN0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH552E       P1.4 / T2_/ CAP1_/ SCS / TIN2 / UCC1 / AIN1 1       P1.5 / MOSI / PWM1 / TIN3 / UCC2 / AIN2 2     VCC / VDD       P1.6 / MISO / RXD1 / TIN4 3     GND / VSS       P1.7 / SCK / TXD1 / TIN5 4     P3.7 / UDM       RST / T2EX_/ CAP2_5     P3.6 / UDP                                                                                                                                                                                                                                                                                      | v <sup>33</sup> 9<br>8<br>7<br>6                         | CH551G<br>P3.2 / INTO 1<br>P1.4 / T2_ / CAP1_ / SCS / TIN2 2 VCC / VDD<br>P1.5 / MOSI / PWM1 / TIN3 3 GND / VSS<br>P1.6 / MISO / TIN4 4 P3.7 / UDM<br>P1.7 / SCK / TIN5 5 P3.6 / UDP<br>RST / T2EX_ / CAP2_6 P3.4 / PWM2 / T0<br>P3.1 / PWM2_/ TXD 7 P3.3 / INT1<br>P3.0 / PWM1_ / RXD 8 P1.1 / T2EX / CAP2 / TIN1                                                                                   |

| Pa | ickage_ | Width o       | f plastic     | Lead pitch    |                      | Package Description      | Ordering |

|----|---------|---------------|---------------|---------------|----------------------|--------------------------|----------|

| TS | SOP-20  | <u>4.40mm</u> | 173mil        | 0.65mm        | 25mil thin c         | ompact 20-pin SMD CH552T |          |

| s  | SOP-16  | 3.9mm         | 150mil        | 1.27mm        | 50mil                | Standard 16-pin SMD      | CH552G   |

| M  | SOP-10  | 3.0mm         | 118mil        | 0.50mm        | <u>19.7mil Minia</u> | ture 10-pin SMD CH552E   |          |

| S  | SOP-16  | 3.9mm         | <u>150mil</u> | <u>1.27mm</u> | 50mil                | Standard 16-pin SMD      | CH551G   |

| 3 |  |

|---|--|

|   |  |

|           | lead <u>Pin numl</u> | <u>per</u> | Pin            | Other features Name                             |                                                                                             |

|-----------|----------------------|------------|----------------|-------------------------------------------------|---------------------------------------------------------------------------------------------|

| TSSOP20 S | P16 MSOF             | 10         | name           | (Left function priority)                        | Other Functional Description                                                                |

| 19        | 15                   | 9          | <u>vcc v</u>   | סס                                              | Power input, requires an external power supply decoupling capacitor 0.1uF.                  |

|           |                      |            |                |                                                 | USB internal regulator power output and the internal USB power input, when the power        |

| 20        | 16                   | 10         | V33            |                                                 | supply is connected the VCC input voltage is less than 3.6V external power supply,          |

|           |                      |            |                |                                                 | external power supply decoupling capacitor 0.1uF when the supply voltage is greater than 3. |

| 18        | 14                   | 8          | <u>GND V</u>   | ss                                              | Common ground.                                                                              |

| 6         | 6                    | 5          | RST RS         | T / T2EX_ / CAP2_ Suffix unde                   | rlined pin mapping of the same name is not underlined pins.                                 |

| 7         | -                    | -          | <u>P1.0</u> T2 | / CAP1 / TIN0                                   | RST pin pull-down resistor; other GPIO default pull-up resistor. RST                        |

|           |                      |            | ]              |                                                 | reset input.                                                                                |

| 8         | 9                    | -          | P1.1 12        | 2EX / CAP2 / TIN1<br>/ VBUS2 / AIN0             | T2: timer / counter external count input / output 2 clocks. T2EX: timer / counter           |

| 17        | -                    | -          | <u>P1.2</u> X  | / RXD_                                          | reload 2 / capture input. CAP1, CAP2: timer / counter 1 input 2 capture. TIN0 ~             |

| 16        | -                    | -          | <u>P1.3</u> X0 | O/TXD_                                          | TIN5: 0 # ~ 5 # capacitance detection touch key input channel. AIN0 ~ AIN3: 0               |

|           |                      |            |                |                                                 | #~3 # channel ADC analog signal input. UCC1, UCC2: USB type-C two-way                       |

| 2         | 2                    | 1          | P1.4 T2        | 2_ / CAP1_ / SCS<br>/ <u>TIN2 / UCC1 / AIN1</u> | channel configuration. VBUS1, VBUS2: USB type-C bus voltage sense input.                    |

|           |                      |            |                |                                                 | XI, XO: external crystal oscillator input terminal, an inverting output terminal.           |

| 3         | 3                    | 2          | P1.5 M         | OSI / PWM1 / TIN3<br>/ UCC2 / AIN2              | RXD, TXD: UART0 serial data input and serial data output. SCS, MOSI, MIS0,                  |

| 4         | 4                    | 3          | P1.6 M         | ISO / RXD1 / TIN4                               | SCK: SPI0 interfaces, SCS is the chip select input, MOSI output host / slave                |

| 5         | 5                    | 4          | P1.7 SC        | 3K / TXD1 / TIN5                                | input, MISO host input / output slave, SCK is a serial clock. PWM1, PWM2:                   |

| 10        | 8                    | -          | P3.0 PV        | M1_/RXD                                         | PWM1 output, PWM2 output. RXD1, TXD1: UART1 serial data input and serial                    |

| 9         | 7                    | -          | <u>P3.1</u> PV | /M2_ / TXD                                      | data output. INT0, INT1: External Interrupt 0, external interrupt 1 input. T0, T1:          |

|           |                      |            |                |                                                 | timer 0, timer 1 external input. UDM, UDP: D-, D + signal terminal of the USB               |

| 1         | 1                    | -          | P3.2 T         | XD1_ / INT0<br>/ VBUS1 / AIN3                   | device. Note: P3.6 and P3.7 V33 as the internal I / O power supply, the high                |

| 11        | 10                   | -          | P3.3 II        | IT1                                             | level only to the input and output voltage V33 does not support 5V                          |

| 12        | 11                   | -          |                | M2 / RXD1_ / T0                                 | 1                                                                                           |

| 13        | -                    | -          | P3.5 T         |                                                 |                                                                                             |

| 14        | 12                   | 6          | P3.6 U         |                                                 | 1                                                                                           |

| 15        | 13                   | 7          | P3.7 U         |                                                 | 1                                                                                           |

| 13        | 13                   | 1          | 1 3.7 0        |                                                 |                                                                                             |

# 5, the SFR

In this manual The register is described The following abbreviations may be used later when:

| abbreviation | description                                                 |

|--------------|-------------------------------------------------------------|

| RO           | It represents the type of access: Read-only                 |

| WO           | Represents Access Type: Write-only, read values are invalid |

| RW           | It represents Access Type: readable and                     |

| writable H   | Its end represents a hexadecimal number B                   |

|              | Its end represents a binary number                          |

# About 5.1 SFR and address distribution

CH552 using the SFR control, management device, and set the operating mode.

80h-FFh occupied SFR address range of the internal data memory space, accessible only via a direct address instruction mode. Wherein the address register x0h or

x8h is bit addressable, so as to avoid access to a specific bit value of bits sometimes modify other; other non-multiple of 8 address registers can only be accessed by byte.

CH552 manual

Data can be written only SFR portion in safe mode, while in non-secure mode is read-only status, for example: GLOBAL\_CFG, CLOCK\_CFG,

WAKE\_CTRL.

SFR portion having one or more aliases, for example: SPI0\_CK\_SE / SPI0\_S\_PRE. Part of the address corresponding to a plurality of individual SFR, for example: SAFE\_MOD / CHIP\_ID, ROM\_CTRL / ROM\_STATUS. CH552 comprising standard SFR registers 8051, while increasing the other control registers. Specific SFR in the table below.

| <u>SFR</u>            | 0,8              | 1,9                 | 2, A          | 3, B                        | 4, C            | 5, D           | 6, E                   | 7, F       |

|-----------------------|------------------|---------------------|---------------|-----------------------------|-----------------|----------------|------------------------|------------|

| 0xF8 <mark>S</mark>   | PIO_STAT         | SPI0_DATA           | SPI0_CTRL     | SPI0_CK_SE SP<br>SPI0_SETUP | 0_S_PRE         |                | RESET_KEEP WD          | DG_COUNT   |

| <u>0xF0</u>           | В                |                     |               |                             |                 |                |                        |            |

| <u>0xE8</u>           | IE_EX            | IP_EX               | UEP4_1_MOD UI | EP2_3_MOD UEP0              | _DMA_L UEP0_DM  | A_H UEP1_DMA_L | UEP1_DMA_H             |            |

| <u>0xE0</u>           | ACC              | USB_INT_EN          | USB_CTRL      | USB_DEV_AD U                | EP2_DMA_L UEP2_ | DMA_H UEP3_DM  | A_L UEP3_DMA_H         |            |

| <u>0xD8</u> U         | SB_INT_FG USB_II | NT_ST USB_MIS_S     | T USB_RX_LEN  |                             | UEP0_CTRL       | UEP0_T_LEN     | UEP4_CTRL              | UEP4_T_LEN |

| <u>0xD0</u>           | PSW              | UDEV_CTRL           | UEP1_CTRL     | UEP1_T_LEN                  | UEP2_CTRL       | UEP2_T_LEN     | UEP3_CTRL              | UEP3_T_LEN |

| <u>0xC8</u>           | T2CON            | T2MOD               | RCAP2L        | RCAP2L                      | TL2             | TH2            | T2CAP1L                | T2CAP1H    |

| <u>0xC0</u>           | SCON1            | SBUF1               | SBAUD1        | TKEY_CTRL                   | TKEY_DATL       | TKEY_DATH      | PIN_FUNC               | GPIO_IE    |

| <u>0xB8</u>           | IP               | CLOCK_CFG           |               |                             |                 |                |                        |            |

| <u>0xB0</u>           | P3               | GLOBAL_CFG          |               |                             |                 |                |                        |            |

| <u>0xA8</u>           | IE               | WAKE_CTRL           |               |                             |                 |                |                        |            |

| 0xA0                  | P2               | SAFE_MOD<br>CHIP_ID | XBUS_AUX      |                             |                 |                |                        |            |

| <u>0x98</u>           | SCON             | SBUF                | ADC_CFG       | PWM_DATA2                   | PWM_DATA1       | PWM_CTRL       | PWM_CK_SE              | ADC_DATA   |

| <u>0x90</u>           | P1               | USB_C_CTRL          | P1_MOD_OC     | P1_DIR_PU                   |                 |                | P3_MOD_OC              | P3_DIR_PU  |

| <u>0x88</u>           | TCON             | TMOD                | TL0           | TL1                         | TH0             | TH1            | ROM_DATA_L RO          | M_DATA_H   |

| 0x80 <mark>A</mark> [ | DC_CTRL          | SP                  | DPL           | DPH                         | ROM_ADDR_L RC   | M_ADDR_H       | ROM_CTRL<br>ROM_STATUS | PCON       |

table 5.1 Special Function can Register Table

Remarks :(1), red text Representative bit addressable; (2), the following is a description corresponding to the color box

| ADC register address register associated SPI0   |

|-------------------------------------------------|

| relevant register Touch-Key USB registers       |

| relevant register associated timer / counter    |

| register 2 associated port registers associated |

| PWM1 and PWM2 associated registers              |

| relevant register UART1 associated registers    |

| Flash-ROM                                       |

|                                                 |

|                                                 |

|                                                 |

5.2 SFR reset values and classification

#### Table 5.2 SFR and reset values described

| Functional Classificat | ion name | address    | description | Reset value       |

|------------------------|----------|------------|-------------|-------------------|

| System Settings        | В        | <u>F0h</u> | B register  | <u>0000 0000b</u> |

| Related register       | ACC      | E0h accu   | nulator     | <u>0000 0000b</u> |

|                                    | PSW        | D0h Prog         | ram Status Register                                         | 0000 0000b        |

|------------------------------------|------------|------------------|-------------------------------------------------------------|-------------------|

|                                    |            |                  | Global configuration register (the bootstrap state CH552)   | 1010 0000b        |

|                                    |            |                  | Global configuration register (the application state CH552) | 1000 0000b        |

|                                    | GLOBAL_CFG | B1h              | Global configuration register (CH551 guided program status) | <u>1110 0000b</u> |

|                                    |            |                  | Global configuration register (the application state CH551) | 1100 0000b        |

|                                    |            |                  | CH552 chip identification code ID (read only)               | 0101 0010b        |

|                                    | CHIP_ID    | A1h              | CH551 chip identification code ID (read only)               | 0101 0001b        |

|                                    | SAFE_MOD   | <u>A1h</u> Secu  | rity Mode Control Register (write only)                     | 0000 0000b        |

|                                    | DPH        | <u>83h</u> Data  | Address Pointer High 8                                      | <u>0000 0000b</u> |

|                                    | DPL        | 82h Data         | Address Pointer Low 8                                       | 0000 0000b        |

|                                    | DPTR       | <u>82h</u>       | DPL and DPH composed of 16 SFR                              | 0000h             |

|                                    | SP         | 81h Stac         | k Pointer                                                   | 0000 0111b        |

|                                    | WDOG_COUNT | <u>FFh</u> Wat   | shdog Count Register                                        | <u>0000 0000b</u> |

| Clock, sleep and                   | RESET_KEEP | <u>FEh</u> Rese  | t the holding registers (the power-on reset state)          | <u>0000 0000b</u> |

| power control                      | CLOCK_CFG  | <u>B9h</u> Syste | m clock configuration register                              | <u>1000 0011b</u> |

| associated registers               | WAKE_CTRL  | <u>A9h</u> Slee  | p wakeup control register                                   | <u>0000 0000b</u> |

|                                    | PCON       | 87h Pow          | er control register (on the lower reset state)              | <u>0001 0000b</u> |

|                                    | IP_EX      | E9h Exter        | ded Interrupt Priority Control Register                     | <u>0000 0000b</u> |

|                                    | IE_EX      | E8h Exter        | ded Interrupt Enable Register                               | <u>0000 0000b</u> |

| Related interrupt control register | GPIO_IE    | <u>C7h</u>       | GPIO interrupt enable register                              | <u>0000 0000b</u> |

|                                    | IP         | B8h Inter        | upt Priority Control Register                               | <u>0000 0000b</u> |

|                                    | IE         | A8h Inter        | upt enable register                                         | <u>0000 0000b</u> |

|                                    | ROM_DATA_H | <u>8Fh</u>       | flash-ROM data register high byte                           | xxxx xxxxb        |

|                                    | ROM_DATA_L | <u>8Eh</u>       | flash-ROM Data Register Low Byte                            | xxxx xxxxb        |

|                                    | ROM_DATA   | <u>8Eh</u>       | ROM_DATA_L and ROM_DATA_H composed of 16 SFR                | xxxxh             |

| Flash-ROM                          | ROM_STATUS | <u>86h</u>       | flash-ROM status register (read only)                       | 0000 0000b        |

| associated registers               | ROM_CTRL   | <u>86h</u>       | flash-ROM control register (write only)                     | <u>0000 0000b</u> |

|                                    | ROM_ADDR_H | <u>85h</u>       | flash-ROM Address Register High Byte                        | xxxx xxxxb        |

|                                    | ROM_ADDR_L | <u>84h</u>       | flash-ROM Address Register Low Byte                         | xxxx xxxxb        |

|                                    | ROM_ADDR   | <u>84h</u>       | ROM_ADDR_L and ROM_ADDR_H composed of 16 SFR                | xxxxh             |

|                                    | PIN_FUNC   | <u>C6h</u> Pin   | Function Select Register                                    | <u>1000 0000b</u> |

|                                    | XBUS_AUX   | <u>A2h</u> Auxil | ary external bus setting register                           | <u>0000 0000b</u> |

|                                    | P3_DIR_PU  | <u>97h</u>       | P3 port direction control and the pullup enable register    | <u>1111 1111b</u> |

| Port-related                       | P3_MOD_OC  | <u>96h</u>       | Port P3 output mode register                                | <u>1111 1111b</u> |

| registers                          | P1_DIR_PU  | <u>93h</u>       | P1 and pull-directional control port enable register        | <u>1111 1111b</u> |

|                                    | P1_MOD_OC  | <u>92h</u>       | Port output mode register P1                                | <u>1111 1111b</u> |

|                                    | P3         | <u>B0h</u>       | Register input and output ports P3                          | <u>1111 1111b</u> |

|                                    | P2         | <u>A0h</u>       | P2 port output register                                     | <u>1111 1111b</u> |

|                                    | P1         | <u>90h</u>       | Input and output ports P1 register                          | <u>1111 1111b</u> |

| Timer / Counter                    | TH1        | <u>8Dh</u>       | Timer1 high byte count                                      | xxxx xxxxb        |

| Associated                         | TH0        | 8Ch              | Timer0 high byte count                                      | <u>xxxx xxxxb</u> |

|                                    | TL1        | <u>8Bh</u>       | Timer1 counter low byte                                     | <u>xxxx xxxxb</u> |

| registers 0 and 1                  |            |                  |                                                             |                   |

| INDO     SPM     TimeO / 1 contol register     0000 0000h       UARTO     SBUF     USA TO data register     0000 0000h       Baside container     SCON     SPM     Control Arginator MATO data register     0000 0000h       Baside container     TCCAPI II     CFM     TimeD control Arginator MATO data register     0000 0000h       TCCAPI II     CFM     TimeD control Arginator MATO data register     0000 0000h       TCCAPI II     CFM     TimeD control Arginator Mato data register Arginator Mato data register     0000 0000h       TCCAPI II     CFM     TimeD control Arginator Mator Mato data register 2 too hyte     0000 0000h       TCCAUNT     CFM     TimeD control Arginator Mator Ma                           |                         | l           | 1              |                                              |                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------|----------------|----------------------------------------------|-------------------|

| UARTO     SBUF     99.     UARTO data register     xxx xxxb,       Baland matter     SCON     98.     Control Register UARTO     0000 0000b,       T2CAP114     CEh     Timer 2 capture a hijb bje data (read-only)     xxx xxxb,       T2CAP114     CEh     Timer 2 capture a hijb bje data (read-only)     xxx xxxb,       T2CAP114     CEh     Timer 2 capture a hijb bje data (read-only)     xxx xxxb,       T2CAP114     CEh     Timer 2 counter hijh bje     0000 0000b,       T122     CDh     Timer 2 counter hijh bje     0000 0000b,       T2CUNIT     CCh     Timer 2 counter hijh bje     0000 0000b,       RCAP21     CAh     RCAP24     0000 0000b,       RCAP21     CAh     RCAP24     0000 0000b,       T2CON     CBh     Timer 2 control Register     0000 0000b,       RCAP21     CAh     RCAP24     0000 0000b,     0000 0000b,       RCAP21     CAh     RCAP24     0000 0000b,     0000 0000b,       RCAP21     CAh     Read-register     0000 0000b,     0000 0000b,       RCAP21     CAh <td></td> <td>TMOD</td> <td><u>89h</u></td> <td>Timer0 / 1 mode register</td> <td>0000 0000b</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         | TMOD        | <u>89h</u>     | Timer0 / 1 mode register                     | 0000 0000b        |

| Bailand randiation     SCON     Spin     Control Regular LARTO     OD00 00000,<br>XXX XXXX       T2CAPTH     CFh     Tree7 capture a bith byth data (read-only)     XXX XXXX       T2CAPTH     CFh     Tree7 capture a bith byth data (read-only)     XXX XXXX       T2CAPTH     CFh     Tree7 capture a bith byth data (read-only)     XXX XXXX       T2CAPTH     CFh     Tree7 capture a bith byth data (read-only)     XXX XXXX       T2CAPTH     CFh     Tree7 capture a bith byth data (read-only)     XXX XXXX       T2CAPTH     CFh     Tree7 capture a bith byth data (read-only)     0000 00000.       T2COUNT     CFh     Tree7 capture data register 2 bith byth     0000 0000.       RCAP2L     CAh     RCAP2L capture data register 2 bith byth     0000 0000.       T2M0D     CFh     Tree7 capture register     0000 0000.       T2M0D     CFh     Tree7 capture register     0000 0000.       T2M0D     CFh     Tree7 capture register     0000 0000.       T2M0D     CFh     SPh Capta     SPh     0000 0000.       associated register     PVM1 Adata register     0000 0000. <t< td=""><td></td><td>TCON</td><td><u>88h</u></td><td>Timer0 / 1 Control Register</td><td>0000 0000b</td></t<>                                                                                                                                                                                                                                                                                                                                                            |                         | TCON        | <u>88h</u>     | Timer0 / 1 Control Register                  | 0000 0000b        |

| TCAP1H     CEh     Timet2 capture a high byte data (read-only)     xxxx xxxxh       T2CAP1L     CEh     Timet2 capture a low-byte data (read-only)     xxxx xxxh       T2CAP1L     CEh     Timet2 capture a low-byte data (read-only)     xxxx xxxh       T12     CCh     Timet2 capture a low-byte data (read-only)     xxxx xxxh       T12     CCh     Timet2 capture a high byte     0000 0000b.       T12     CCh     Timet2 counter high byte     0000 0000b.       T2COUNT     CCh     Timet2 counter clow     0000 0000b.       RCAP2L     CAB     Timet2 control register     0000 0000b.       RCAP2L     CAB     RCAP2L     CAB     0000 0000b.       RCAP2L     CAB     Timet2 control register     0000 0000b.     0000 0000b.       RCAP2L     CAB     Timet2 control register     0000 0000b.     0000 0000b.       RCAP2L     CAB     Timet2 control register     0000 0000b.     0000 0000b.       RCAP2L     PVML CRS     PEh     ObCh Vicker PVM actina register     0000 0000b.     0000 0000b.       sascitated register     PVML CRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UART0                   | SBUF        | <u>99h</u>     | UART0 data register                          | <u>xxxx xxxxb</u> |

| TCAP1L     SEI     Time2 capture a low-byte data (read only)     xxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Related register        | SCON        | <u>98h</u>     | Control Register UART0                       | 0000 0000b        |

| Time?     Time?     Scooth     Scooth       TH2     CD.     Time? Counter high byte     0000 0000b       TL2     CD.     Time? Counter high byte     0000 0000b       TRCAUPI     CD.     Time? Counter high byte     0000 0000b       RCAP2I     CD.     Time? Counter high byte     0000 0000b       RCAP2I     CD.     RCAP2I     0000 0000b       RCAP2I     CD.     RCAP2I     0000 0000b       RCAP2I     CD.     RCAP2I and RCAP2I |                         | T2CAP1H     | <u>CFh</u>     | Timer2 capture a high byte data (read-only)  | <u>xxxx xxxxb</u> |

| TH2     CDh     Timer 2 counter high byte     0000 0000b       Timer / Counter relater     TL2     CCh     Timer 2 counter Low     0000 0000b       TCOUNT     CCh     TL2 and TH2 composed of 18 SFR     0000 0000b       RCAP2H     Caba Rest do count / capture data register 2 high byte     0000 0000b       RCAP2L     Caba Rest do count / capture data register 2 high byte     0000 0000b       RCAP2     Caba Rest do count / capture data register 2 high byte     0000 0000b       TAMOO     Caba     RCAP2L and CRAP2 Home Cast register     0000 0000b       TAMOO     Caba     Timer 2 conder degister     0000 0000b       TAMOO     Caba     Timer 2 conder degister     0000 0000b       associatad register     PVML CrEL     SPL     Cock Divider PVM data register     0000 0000b       associatad register     PVML DATA2     SPL     SPL     SPL     SPL     SPL       SPL0 SETUP     PCh     SPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         | T2CAP1L     | <u>CEh</u>     | Timer2 capture a low-byte data (read only)   | <u>xxxx xxxxb</u> |

| TL2     CCA     Time? Counter Low     0000 0000b,       registers 2     RCAP2H     CEAn     TL2 and TH2 composed of 16 SFR     0000 0000b,       RCAP2H     CEAn Res     0000 0000b,     0000 0000b,     0000 0000b,       RCAP2L     CEAn Res     0000 0000b,     0000 0000b,     0000 0000b,       RCAP2L     CEAn     RCAP2L     0000 0000b,     0000 0000b,       T2K0D     CSB     Time? Control Register     0000 0000b,     0000 0000b,       T2CON     CSB     Time? Control Register     0000 0000b,     0000 0000b,       PVM1 and PVM2     PVM, CrTRL     9Dh     PVM2 corrol Register     0000 0000b,       gestore     PVM, DATA1     9Ch     PVM2 clast register     0000 0000b,       SPI0 SETUP     FCh     SPI0 data register     0010 0000b,     0000 0000b,       SPI0 SETUP     FCh     SPI0 data register     0010 0000b,     0000 0000b,       SPI0 SETUP     FCh     SPI0 data register     0010 0000b,     0000 0000b,       SPI0 SETUP     FCh     SPI0 data register     0010 0000b,     0000 0000b,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         | T2CAP1      | <u>CEh</u>     | T2CAP1L and T2CAP1H composed of 16 SFR       | xxxxh             |

| Time / Counter relate:     T2COUNT     C/L     IL2 and TH2 composed of 19 SFR     0000h       register 2     RCAP2H     GBb Rel     Gab Rel     0000 0000b     0000 0000b       RCAP2L     GBb Rel     Gab Rel     Gab Rel     0000 0000b     0000 0000b       RCAP2L     GAb     RCAP2L     GAb     RCAP2L     0000 0000b       RCAP2     GAb     RCAP2L     GAb     RCAP2L     0000 0000b       Time2 Control Register     0000 0000b     0000 0000b     0000 0000b     0000 0000b       PVMA I and PVML2     PVM. Critt     9Dh     PVMC Control Register     0000 0000b     0000 0000b       PVMA1 and PVML2     PVM. DATA1     9Ch     PVMC data register     0000 0000b     0000 00000b     0000 0000b     0000 0000b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         | TH2         | <u>CDh</u>     | Timer2 counter high byte                     | 0000 0000b        |

| T2COUNT     CCD     T12 at T12 composed of 15 SFR     0000h       RCAP2H     GBL Res     down't capture data register 2 high byte     0000 0000b;       RCAP2L     GAN Res     ecount / capture data register 2 high byte     0000 0000b;       RCAP2     GAN     RCAP2L     GAN     0000 0000b;       RCAP2     GAN     RCAP2L     0000 0000b;     0000 0000b;       RCAP2     GAN     RCAP2L composed of 16 SFR     0000 0000b;       T2000     GSN     Timer2 mode register     0000 0000b;       PVM1 and PVM2     PVM, CrRL     9Eh     Clock Dvider PVM setting register     0000 0000b;       gasociated register     PVM, DATA1     9Ch     PVM data register     0000 0000b;       gasociated register     SPI0 SETUP     FCh     SPI0 seture mode preset data register     0000 0000b;       gasociated register     SPI0 CrRL     FAh     Central Register SPI0     0000 0000b;       SPI0 JCTRL     FSh     SPI0 data transceiver register     0001 0000b;     0001 0000b;       SPI0 CrRL     FSh     SPI0 data transceiver register     xoxx xoxb;     xoxx xoxb; </td <td>Timer / Counter related</td> <td></td> <td><u>CCh</u></td> <td>Timer2 Counter Low</td> <td>0000 0000b</td>                                                                                                                                                                                                                                                                                                                                                                        | Timer / Counter related |             | <u>CCh</u>     | Timer2 Counter Low                           | 0000 0000b        |

| RCAP2H     CBh Pelast count / capture data register 2 lwip byte     0000 0000b,       RCAP2L     CAh     RCAP2L count / capture data register 2 lwip byte     0000 000b,       RCAP2L     CAh     RCAP2L and RCAP2L and RCAP2H composed of 16 SFR     0000 000b,       T2000     C9h     Timer2 Control Register     0000 000b,       T2000     C9h     Timer2 Control Register     0000 000b,       PWM1 and PWM2     PVM, CK, SE     9Eh     Coch Didder PWM setting register     0000 000b,       sesociated registor     PVM, CK, SE     9Eh     PVM data register     0000 000b,       sesociated registor     PVM, DATA2     9Eh     PVM data register     0000 000b,       sesociated registor     PVM, DATA2     9Eh     SPI0 setting register     0010 000b,       SPI0 SETUP     FCh     SPI0 setting register     0010 000b,     0010 000b,       sesociated registor     SPI0, CR, E     EBh     SPI0 setting register     0000 010b,       sesociated registor     SPI0, CR, E     EBh     SPI0 setting register     0000 010b,       sesociated registor     SPI0, CR, E     EBh     SPI0 setting regist                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |             | <u>CCh</u>     | TL2 and TH2 composed of 16 SFR               | 0000h             |

| RCAP2     CAP     RCAP2L and RCAP2H composed of 16 SFR     0000h       T2MOD     C9h     Timer2 mode register     0000 0000b       T2CON     C8h     Timer2 Control Register     0000 0000b       PVML1 and PVMU2     PVM_CK.SE     9Eh     Clock Divider PVM setting register     0000 0000b       PVML1 and PVMU2     PVM_CK.SE     9Eh     Clock Divider PVM setting register     0000 0000b       associated register     PVM_DATA2     9Bh     PVM/M data register     0000 0000b       SPI0 SETUP     FCh     SPI0 setting register     0001 0000b     0000 0010b       SPI0 CTRL     FAh     Control Register SPI0     0001 0000b     0000 0010b       SPI0 STAT     FBh     SPI0 dack divider setting register     0010 0000b     0000 0010b       SPI0_STAT     FBh     SBuff 1     C1h     UART1 data register SPI0     0000 0000b       MACT relevant     SGON1     C2h     UART1 data register     xxxx xxxxb       MACT relevant     ADC control Register UAR11     0100 0000b     xxxx xxxb       MACT relevant     ADC Control Register     SPI0     0000 000xb<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         | RCAP2H      | CBh Relo       | ad count / capture data register 2 high byte | 0000 0000b        |

| T2MOD     CBA     Timer2 mode register     0000 0000h       T2CON     CBA     Timer2 control Register     0000 0000h       PWM1 and PVM2     PVM.CK.SE     9Eh     Ciock Divder PVM setting register     0000 0000h       associated register     PVM.DATA1     9Ch     PVM.M control Register     0000 0000h       pWM.DATA2     9Bh     PVM.Control Register     XXX XXXXb       pVM.DATA2     9Bh     PVM.Control Register     XXX XXXb       pVM.DATA2     9Bh     PVM.Control Register     XXX XXXb       pVM.DATA2     9Bh     PVM.Control Register     0000 0000h       sPIO.S.FRE     FBh     SPIO satura register     0000 0000h       sPIO.S.FRE     FBh     SPIO data transceiver register     0000 0000h       sPIO.CK.SE     FBh     SPIO data transceiver register     XXX XXxb       SPIO.CK.SE     FBh     SPIO data transceiver register     XXX XXxb       UART1     SSIO     Control Register SPIO     0000 0100h     XXX XXxb       sassociated register     SOLO_DATA     SPIO     ADC control Register     XXX XXxb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         | RCAP2L      | CAh Relo       | ad count / capture data register 2 low byte  | 0000 0000b        |

| TZCON     CBA     Timer2 Control Register     0000 000b       PVM.1 and PVM.1     PVM.CTRL     9Dh     PVM.0 Control Register     0000 0010b       associated registers     PVM.DATA1     9Ch     PVM.1 data register     0000 000b       PVM.DATA2     9Bh     PVM.1 data register     xxxx xxxxb       PVM.DATA2     9Bh     PVM.2 data register     0000 000b       SPI0 SETUP     FCh     SPI0 setting register     0010 000b       SPI0 relevant     SPI0.CK.SE     FBh     SPI0 clock divider setting register     0010 000b       SPI0_CTRL     FAh     Control Register SPI0     0000 0010b     0000 001b       SPI0_STAT     FBh     SPI0 clock divider setting register     0000 000b     0000 000b       SPI0_STAT     FBh     SPI0 clock divider setting register     0000 000b     0000 000b       ADC relevant     ADC_DATA     FBh     SPI0 data transcriver register     xxxx xxxb       ADC relevant     ADC_CATA     FBh     ADC data register     xxxx xxxb       ADC relevant     ADC_CATA     SPI     ADC control Register UART1     0000 000b </td <td>RCAP2</td> <td><u>CAh</u></td> <td>RCAP2L and RCAP2H composed of 16 SFR</td> <td>0000h</td>                                                                                                                                                                                                                                                                                                                                                                                                   |                         | RCAP2       | <u>CAh</u>     | RCAP2L and RCAP2H composed of 16 SFR         | 0000h             |

| PVM. CK_SE     9Eh     Clock Divider PVM setting register     0000 0000b       associated register     PVM. CTRL     9Dh     PVM. Control Register     0000 0000b       associated register     PVM. DATA1     9Ch     PVM. Control Register     0000 0000b       PVM. DATA2     9Bh     PVM. Control Register     0000 0000b     0000 0000b       SPI0 SETUP     FCh     SPI0 setting register     0000 0000b     0000 0000b       SPI0 relevant     SPI0 CTRL     FBh     SPI0 clock divider setting register     0010 0000b       SPI0 DATA     F9h     SPI0 data transceiver register     0010 0000b     0000 0000b       SPI0 JATA     F9h     SPI0 data transceiver register     0000 0000b     0000 0000b       ADC TRL     F8h     Status Register SPI0     0000 0000b     0000 0000b       ADC TRL     CAh     CAh     CAh     0000 0000b     0000 0000b       ADC relevant     ADC_CATA     9Fh     ADC control Register     0000 0000b     0000 0000b       ADC_CATA     9Fh     ADC control Register     0000 0000b     00000 0000b     00000 0000b     00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         | T2MOD       | <u>C9h</u>     | Timer2 mode register                         | 0000 0000b        |

| PWM1 and PWM2     PWM. CTRL     9Dh     PWM2 Control Register     0000 0010b       associated register     PWM_DATA2     9Bh     PWM2 data register     xxx xxxxb       PWM_DATA2     9Bh     PWM2 data register     0000 0000b       PWM_DATA2     9Bh     PWM2 data register     0000 0000b       SPI0 SETUP     FCh     SPI0 setting register     0010 0000b       SPI0 CREVAT     SPI0 CREXE     EBh     SPI0 clock divider setting register     0010 0000b       SPI0 CREVAT     FAh     Control Register SPI0     0000 0010b     0000 0010b       SPI0 DATA     F9h     SPI0 data transceiver register     xxxx xxxb     0000 000b       JUART1     SBAUD1     C2h     UART1 data register SPI0     0000 1000b       JUART1     SBUF1     C1h     UART1 data register     xxxx xxxb       ADC relevart     ADC_CATA     9Fh     ADC data register     xxxx xxxb       ADC_CRE     S0h     ADC control Register     xxxx xxxb       ADC_CREVA     S0h     ADC control Register     xxxx xxxb       ADC_CREVA     S0h     ADC co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         | T2CON       | <u>C8h</u>     | Timer2 Control Register                      | 0000 0000b        |

| associated register     PVM_DATA1     9Ch     PVM11 data register     xxx xxxxh       PVM_DATA2     9Bh     PVM02 data register     xxx xxxxh       SPI0 SETUP     FCh     SPI0 setting register     0000 0000h       SPI0 relevant     SPI0 CK SE     FBh     SPI0 clock divider setting register     0010 0000h       SPI0 CTRL     FAh     Control Register SPI0     0000 0000h     0000 000h       SPI0 STAT     FBh     SPI0 data transceiver register     xxx xxxxh       VART1     SBAUD1     C2h     UART1 bad rate setting register     0000 0000h       UART1     SBUF1     C1h     UART1 bad rate setting register     xxx xxxxh       ADC relevant     ADC_CFG     9Ah     ADC configuration register     xxxx xxxh       register     ADC_CTRL     8Dh     ADC configuration register     x000 0000h       register     ADC_CTRL     8Dh     ADC configuration register     x000 0000h       register     ADC_CTRL     8Dh     ADC configuration register     x000 0000h       register     KEY_DATL     C4h     Touch-Key low-byte data (read only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         | PWM_CK_SE   | <u>9Eh</u>     | Clock Divider PWM setting register           | 0000 0000b        |

| PVML DATA29BhPVM2 data registerxxx xxxxhSPI0_SETUPFChSPI0 setting register0000 0000bSPI0_SETUPFChSPI0 setting register0010 0000bSPI0_CK_SEFBhSPI0 clock divider setting register0010 0000bSPI0_CTRLFAhControl Register SPI00000 0000bSPI0_STATFBhSPI0 data transceiver register0000 0000bSPI0_STATFBhStatus Register SPI00000 0000bAUT1SBU1C2hUART1 baud rate setting register0000 0000bUART1SBU1C2hUART1 baud rate setting registerxxx xxxxbADC_DATAFBhStatus Register SPI00000 0000bADC_CTRLSCN1C0hControl Register SPI00000 0000bADC_DATASFhADC data transceiver registerxxx xxxxbADC_DATASFhADC data registerxxx xxxxbADC_DATASFhADC control Register UART10100 0000bADC_CFGSAhADC control Registerxxx xxxxb0000 0000bTouch-KeyTKEY_DATHC5hTouch-Key high byte data (read-only)0000 0000bTouch-KeyTKEY_DATC4hTKEY_DATH composed of 16 SFR00xxhUSB relatedUEP1 DMA_LEEh control Hegisterxxx xxxxb0000 00xbUSB relatedUEP1_DMA_LEEh control and 4 buffer stat address high byte0000 00xbUSB relatedUEP1_DMA_LEEh control and 4 buffer stat address high byte0000 00xbUSB relatedUEP0_DMA_L<                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PWM1 and PWM2           | PWM_CTRL    | <u>9Dh</u>     | PWM Control Register                         | 0000 0010b        |

| SPI0 relevantSPI0 SETUP<br>SPI0_S_PREFChSPI0 setting register0000 0000bSPI0_S_PREFBhSPI0 slave mode preset data register0010 0000bregisterSPI0_CTRLFAhControl Register SPI00000 0000bSPI0_DATAF9hSPI0 data transceiver register0000 0000bSPI0_STATF8hStilu segister SPI00000 0000bUART1SBAUD1C2hUART1 baud rate setting registerxxxx xxxxbSBAUD1C2hUART1 data registerxxxx xxxbSBAUD1C2hUART1 data registerxxxx xxxbADC_DATASFhADC control Register SPI00000 0000bADC_CATASPhControl Register ART101100 0000bADC_DATASFhADC control Registerxxxx xxxbADC_OFGSAhADC control Registerxxxx xxxbADC_CFGSAhADC control Registerx000 0000bTouch-KeyTKEY_DATLC5hTouch-Key high byte data (read-only)0000 0000bTouch-KeyTKEY_DATLC4hTKEY_DATL and TKEY_DATH composed of 16 SFR00xxhUSB relatedUEP1_DMA_LEEh EndUEP1_DMA_L and UEP1_DMA_L and UEP1_DMA_L composed of 16 SFR0xxhUSB relatedUEP0_DMA_LECh_EndUEP1_DMA_L and UEP1_DMA_L and other start address low bytexxxx xxxxbUSB relatedUEP0_DMA_LECh_EndUEP1_DMA_L and UEP1_DMA_L and DEP1_DMA_L and other start address low bytexxxx xxxxbUSB relatedUEP0_DMA_LECh_EndUEP1_DMA_L and UEP0_DMA_L and DEP0_DMA_L and DE                                                                                                                                                                                                                                                                                                                                                                                                           | associated registers    | PWM_DATA1   | <u>9Ch</u>     | PWM1 data register                           | <u>xxxx xxxxb</u> |

| SPI0 S_PRE     FBh     SPI0 slave mode preset data register     0010 0000h       SPI0 cRv set     FBh     SPI0 clock divider setting register     0010 0000h       SPI0_CTRL     FAh     Control Register SPI0     0000 0010h       SPI0_DATA     F9h     SPI0 data transceiver register     xxxx xxxxb       SPI0_STAT     F8h     Status Register SPI0     0000 1000h       UART1     SBAUD1     C2h     UART1 data register     xxxx xxxb       SBUF1     C1h     UART1 data register     xxxx xxxb       SCON1     C0h     Control Register UART1     0100 0000h       ADC_relevant     ADC_CFG     9Ah     ADC data register     xxxx xxxb       ADC_CTRL     80h     ADC control Register     x000 0000h       register     ADC_CTRL     80h     ADC control Register     x000 0000h       Touch-Key     TKEY_DATL     C5h     Touch-Key Idv byte data (read-only)     0000 0000h       associated register     TKEY_DATL     C4h     TKEY_DATL     C4h     Touch-Key Idv byte data (read-only)     xxxx xxxb       usesciated register     TKEY_DATL <td></td> <td>PWM_DATA2</td> <td><u>9Bh</u></td> <td>PWM2 data register</td> <td><u>xxxx xxxxb</u></td>                                                                                                                                                                                                                                                                                                                                                                                                        |                         | PWM_DATA2   | <u>9Bh</u>     | PWM2 data register                           | <u>xxxx xxxxb</u> |

| SPI0 relevant<br>register     SPI0_CK_SE<br>SPI0_CTRL     FBh<br>FAh<br>FAh     Control Register SPI0     0010 000b<br>0000 010b       SPI0_DATA     F9h<br>SPI0_DATA     F9h<br>F9h     SPI0 data transceiver register     xxxx xxxxb       SPI0_STAT     F8h     Status Register SPI0     0000 0100b       UART1     SBAUD1     C2h     UART1 baud rate setting register     xxxx xxxxb       SBUF1     C1h     UART1 data register     xxxx xxxxb     0100 000b       ADC_DATA     9Fh     ADC data register     xxxx xxxb     0100 000b       ADC_relevant<br>register     ADC_DATA     9Fh     ADC control Register UART1     0100 000b       ADC_rEGG     9Ah     ADC control Register     x000 0000b     xxx xxxxb       ADC_CTRL     80h     ADC control Register     x000 0000b       Touch-Key     TKEY_DATL     C4h     Touch-Key low byte data (read-only)     0000 0000b       associated registers     TKEY_DATL     C4h     Touch-Key low-byte data (read only)     xxxx xxxxb       userciated register     VEP_DAT     C4h     Touch-Key low-byte data (read-only)     0000 000xb       userciated register                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         | SPI0_SETUP  | <u>FCh</u>     | SPI0 setting register                        | 0000 0000b        |

| registerSPI0_CTRLFAhControl Register SPI00000 0010bSPI0_DATAF9hSPI0 data transceiver registerxxxx xxxxbSPI0_STATF8hStatus Register SPI00000 1000bUART1SBAUD1C2hUART1 baud rate setting registerxxxx xxxxbBSUF1C1hUART1 data registerxxxx xxxxbSCON1C0hControl Register UART10100 0000bADC_DATA9FhADC data registerxxxx xxxxbADC_CFG9AhADC control Register0000 0000bADC_CTRL80hADC control Register0000 0000bADC_CTRL80hADC control Registerx000 0000bTouch-KeyTKEY_DATHC5hTouch-Key high byte data (read-only)0000 0000bassociated registerTKEY_DATLC4hTKEY_DATL and TKEY_DATL composed of 16 SFR00xxhUSB relatedUEP1_DMA_HEEh EndUEP1_DMA_H composed of 16 SFR0xxkhUSB relatedUEP0_DMA_LEEh EndUEP1_DMA_H composed of 16 SFR0xxkhUSB relatedUEP0_DMA_LEEh EndUEP1_DMA_H composed of 16 SFR0xxxhUEP1_DMA_LEEh EndUEP1_DMA_H composed of 16 SFR0xxxhUEP0_DMA_LEEh EndUEP0_DMA_L and UEP1_DMA_H composed of 16 SFR0xxxhUEP0_DMA_LEEh EndUEP0_DMA_L and 4 buffer start address high byte0000 00xbUEP0_DMA_LECh_EndUEP0_DMA_L and UEP0_DMA_H composed of 16 SFR0xxxhUEP0_DMA_LECh_EndUEP0_DMA_L and UEP0_DMA_H composed of 16 SFR <td< td=""><td></td><td>SPI0_S_PRE</td><td><u>FBh</u></td><td>SPI0 slave mode preset data register</td><td>0010 0000b</td></td<>                                                                                                                                                                                                                                                                                                            |                         | SPI0_S_PRE  | <u>FBh</u>     | SPI0 slave mode preset data register         | 0010 0000b        |

| SPI0_DATA     F9h     SPI0 data transceiver register     XXX XXXb       SPI0_STAT     F8h     Status Register SPI0     0000 1000b       UART1     SBAUD1     C2h     UART1 baud rate setting register     XXXX XXXb       associated registers     SBUF1     C1h     UART1 data register     XXXX XXXb       ADC_DATA     SUF1     C1h     UART1 data register     XXXX XXXb       ADC_DATA     SC0N1     C0h     Control Register UART1     0100 0000b       ADC_DATA     SFh     ADC data register     XXXX XXXb     XXXX XXXb       ADC_CFG     SAh     ADC control Register     X00 0000b     XXXX XXXb       ADC_CFG     SAh     ADC control Register     X00 0000b     XXXX XXXb       Touch-Key     TKEY_DATH     C5h     Touch-Key logh byte data (read-only)     XXXX XXXxb       associated register     TKEY_DAT     C4h     Touch-Key logh-byte data (read-only)     XXXX XXXb       associated register     TKEY_DAT     C4h     TKEY_DAT     C4h     Touch-Key logh-byte data (read-only)     XXXX XXXb       uspociated register     UEP1_DMA_H <td>SPI0 relevant</td> <td>SPI0_CK_SE</td> <td><u>FBh</u></td> <td>SPI0 clock divider setting register</td> <td>0010 0000b</td>                                                                                                                                                                                                                                                                                                                                                                             | SPI0 relevant           | SPI0_CK_SE  | <u>FBh</u>     | SPI0 clock divider setting register          | 0010 0000b        |

| SPI0_STATF8hStatus Register SPI00000 1000hUART1SBAUD1C2hUART1 baud rate setting registerxxxx xxxxbSBUF1C1hUART1 data registerxxxx xxxbassociated registersSCON1C0hControl Register UART10100 0000hADC patra9FhADC data registerxxxx xxxxb0000 1000hADC_CFG9AhADC configuration register0000 0000hADC_CTRL80hADC control Registerx000 0000hADC_CTRL80hADC control Registerx000 0000hTouch-KeyTKEY_DATHC5hTouch-Key ligh byte data (read-only)0000 0000hTouch-KeyTKEY_DATLC4hTouch-Key low-byte data (read-only)xxxx xxxbassociated registerTKEY_DATLC4hTouch-Key control Register0000 000bhTKEY_DATLC4hTouch-Key Control Registerx000 000bhxxx xxxbUEP1_DMA_HEFh Endorint 1 buffer start address high byte0000 000xbhxxx xxxxbUSB relatedUEP0_DMA_LEEh Endorint 1 buffer start address low bytexxx xxxxbxxx xxxxbUEP0_DMA_LECh Endorint 0 and 4 buffer start address low bytexxx xxxxb0000 00xxbUEP0_DMA_LECh Endorint 0 and 4 buffer start address low bytexxx xxxxb0000 00xxbUEP0_DMA_LECh Endorint 0 and 4 buffer start address low bytexxx xxxxb0000 00xxbUEP0_DMA_LECh Endorint 0 and 4 buffer start address low bytexxx xxxxb0000 00xxbUEP0_DMA_LECh Endorint 0 and 4 buffer s                                                                                                                                                                                                                                                                                                                                                                                        | register                | SPI0_CTRL   | FAh            | Control Register SPI0                        | 0000 0010b        |

| UART1<br>associated registerSBAUD1C2hUART1 baud rate setting registerXXX XXXbssociated registerSBUF1C1hUART1 data registerXXX XXXbADCSCON1C0hControl Register UART10100 0000bADC relevant<br>registerADC_CFG9AhADC configuration register0000 0000bADC_CTRL80hADC control RegisterX000 0000bTouch-KeyTKEY_DATHC5hTouch-Key high byte data (read-only)0000 0000bTouch-KeyTKEY_DATLC4hTKEY_DATL control Register0000 0000bTouch-KeyTKEY_DATLC4hTKEY_DATL control Register0000 0000bTKEY_DATLC4hTKEY_DATL control Register0000 0000bVEP1_DMA_HEFh Endpoint 1 buffer start address high byte0000 000xbUSB relatedUEP1_DMA_LEEh Endpoint 1 buffer start address low byteXXXX XXXbUSB relatedUEP0_DMA_HECh expoint 0 and 4 buffer start address high byte0000 000xbUEP0_DMA_LECh expoint 0 and 4 buffer start address low byteXXXX XXXbUEP0_DMA_LECh expoint 0 and 4 buffer start address low byteXXXX XXXbUEP0_DMA_LECh expoint 0 and 4 buffer start address low byteXXXX XXXbUEP0_DMA_LECh expoint 0 and 4 buffer start address low byteXXXX XXXbUEP0_DMA_LECh expoint 0 and 4 buffer start address low byteXXXX XXXbUEP0_DMA_LECh expoint 0 and 4 buffer start address low byteXXXX XXXbUEP0_DMA_LECh expoint 0 and 4 buffer start address low byte                                                                                                                                                                                                                                                                                                                           |                         | SPI0_DATA   | <u>F9h</u>     | SPI0 data transceiver register               | <u>xxxx xxxxb</u> |

| UART1<br>associated registersSBUF1C1h<br>C1hUART1 data registerXXXX xxxxbassociated registersSCON1C0hControl Register UART10100 0000bADC relevant<br>registerADC_DATA9FhADC data registerXXXX XXXbADC relevant<br>registerADC_CFG9AhADC configuration register0000 0000bADC_CTRL80hADC configuration register0000 0000bTouch-KeyTKEY_DATHC5hTouch-Key high byte data (read-only)0000 0000bTouch-KeyTKEY_DATLC4hTouch-Key low-byte data (read-only)XXXX XXxbassociated registerTKEY_DATC4hTKEY_DATL and TKEY_DATH composed of 16 SFR000xhTKEY_CTRLC3hTouch-Key Control Register0000 000xbXXXX XXxbUEP1_DMA_LEEh End point 1 buffer start address low byteXXXX XXxb0000 000xbUSB relatedUEP0_DMA_LEEh End point 0 and 4 buffer start address low byteXXXX XXxxbUEP0_DMA_LECh End point 0 and 4 buffer start address low byteXXXX XXxxbUEP0_DMA_LECh End point 0 and 4 buffer start address low byteXXXX XXXbUEP0_DMA_LECh End point 0 and 4 buffer start address low byteXXXX XXxbUEP0_DMA_LECh End point node control register 30000 000xbUEP0_DMA_LECh End point mode control register 30000 000xb                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         | SPI0_STAT   | <u>F8h</u>     | Status Register SPI0                         | 0000 1000b        |

| SBUF1C1hUART1 data registerXXX XXXbassociated registerSCON1COhControl Register UART10100 0000bADC_DATA9FhADC data registerXXXX XXXbADC_CFG9AhADC configuration register0000 0000bADC_CTRL80hADC control RegisterX000 0000bADC_CTRL80hADC control RegisterX000 0000bTouch-KeyTKEY_DATHC5hTouch-Key high byte data (read-only)0000 0000bTouch-KeyTKEY_DATLC4hTouch-Key low-byte data (read only)XXXX XXxbassociated registerTKEY_DATC4hTouch-Key Control Register0000 000xbTKEY_DATC4hTouch-Key Control RegisterX000 000bXXXX XXxbUEP1_DMA_LEFh End<br>UEP1_DMA_LEfh End<br>oint 1 buffer start address high byte0000 000xbUSB relatedUEP1_DMA_LEEh_End<br>Dint 1 buffer start address high byte0000 000xbUEP0_DMA_LECh End<br>UEP1_DMA_LECh End<br>Dint 0 and 4 buffer start address high byte0000 000xbUEP0_DMA_LECh End<br>UEP0_DMA_LECh End<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         | SBAUD1      | <u>C2h</u>     | UART1 baud rate setting register             | <u>xxxx xxxxb</u> |

| SCON1COhControl Register UART10100 0000bADC_DATA9FhADC data registerxxxx xxxbADC_CFG9AhADC configuration register0000 0000bADC_CTRL80hADC control Registerx000 0000bADC_CTRL80hADC control Register0000 0000bTKEY_DATHC5hTouch-Key high byte data (read-only)0000 0000bTKEY_DATLC4hTouch-Key low-byte data (read-only)xxxx xxxbassociated registerTKEY_DATC4hTKEY_DATH composed of 16 SFR00xxhTKEY_DATC4hTKEY_DATL and TKEY_DATH composed of 16 SFR0000 000bbTKEY_CTRLC3hTouch-Key Control Registerx000 0000bUEP1_DMA_HEEh end oint 1 buffer start address low bytexxxx xxxbUSB relatedUEP1_DMA_LEEh oint 1 buffer start address low bytexxxx xxxbUSB relatedUEP0_DMA_HEDh end oint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh oint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh oint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh oint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh oint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh oint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh oint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh oint 0 and 2 buffer start address low bytexxxx xxxbUEP0_DMA_LECh oint 0 an                                                                                                                                                                                                                                                                                                                                           |                         | SBUF1       | <u>C1h</u>     | UART1 data register                          | <u>xxxx xxxxb</u> |

| ADC relevant<br>registerADC_CFG9AhADC configuration register0000 0000bADC_CTRL80hADC control Registerx000 0000bADC_CTRL80hADC Control Registerx000 0000bTouch-KeyTKEY_DATHC5hTouch-Key high byte data (read-only)0000 0000bassociated registersTKEY_DATLC4hTouch-Key low-byte data (read only)xxxx xxxxbassociated registersTKEY_DATC4hTKEY_DATL and TKEY_DATL composed of 16 SFR00xxhTKEY_CTRLC3hTouch-Key Control Registerx000 0000bxxxx xxxbUEP1_DMA_HEFh Endpoint 1 buffer start address high byte0000 00xxbxxxx xxxbUSB relatedUEP1_DMA_LEEh Endpoint 0 and 4 buffer start address high byte0000 00xxbregistersUEP0_DMA_LECh Endpoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh Endpoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh Endpoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh Endpoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh Endpoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh Endpoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh Endpoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh Endpoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh Endpoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh Endpoi                                                                                                                                                                                                                                                                                      | associated registers    | SCON1       | <u>C0h</u>     | Control Register UART1                       | 0100 0000b        |

| ADC_CFG9AhADC configuration register0000 0000bADC_CTRL80hADC control Registerx000 0000bTMEY_DATHC5hTouch-Key high byte data (read-only)0000 0000bTouch-KeyTKEY_DATLC4hTouch-Key low-byte data (read-only)xxxx xxxxbassociated registersTKEY_DATC4hTwee-Key low-byte data (read-only)xxxx xxxbTKEY_DATC4hTwee-Key low-byte data (read-only)xxxx xxxbTKEY_DATC4hTwee-Key Control Register0000 0000bTKEY_CTRLC3hTouch-Key Control Registerx000 0000bUEP1_DMA_HEFh End point 1 buffer start address high byte0000 00xxbUEP1_DMA_LEEh End point 1 buffer start address low bytexxxx xxxbUSB relatedUEP0_DMA_HEDh End point 0 and 4 buffer start address high byte0000 00xxbUEP0_DMA_LECh End point 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh End point 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh End point 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh End point 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh End point 0 and 4 buffer start address low byte0000 000xbUEP0_DMA_LECh End point 0 and 4 buffer start address low byte0000 000xbUEP0_DMA_LECh End point 0 and 4 buffer start address low byte0000 000xbUEP0_DMA_LECh End point 0 and 4 buffer start address low byte0000 000xbUEP0_DMA_LECh End point 0 an                                                                                                                                                                                                                                                                                     |                         | ADC_DATA    | <u>9Fh</u>     | ADC data register                            | <u>xxxx xxxxb</u> |

| ADC_CTRL80hADC Control Registerx000 0000bTKEY_DATHC5hTouch-Key high byte data (read-only)0000 0000bTouch-KeyTKEY_DATLC4hTouch-Key low-byte data (read only)xxxx xxxxbassociated registerTKEY_DATC4hTKEY_DATL and TKEY_DATH composed of 16 SFR00xxhTKEY_CTRLC3hTouch-Key Control Registerx000 000xbxxxx xxxbUEP1_DMA_HEFh EndTouch-Key Control Registerx000 000xxbUEP1_DMA_LEEh Endint 1 buffer start address high byte0000 00xxbUSB relatedUEP0_DMA_LEEhoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxx xxxbUEP0_DMA_LECh_Endoint 0 and 4 buffer start address low bytexxxxUEP0_DMA_E <td< td=""><td></td><td>ADC_CFG</td><td><u>9Ah</u></td><td>ADC configuration register</td><td>0000 0000b</td></td<>                                                                                                                                                                                                                               |                         | ADC_CFG     | <u>9Ah</u>     | ADC configuration register                   | 0000 0000b        |

| Touch-Key   TKEY_DATL   C4h   Touch-Key low-byte data (read only)   xxxx xxxb     associated registers   TKEY_DAT   C4h   Touch-Key low-byte data (read only)   xxxx xxxb     TKEY_DAT   C4h   TKEY_DATL and TKEY_DATH composed of 16 SFR   00xxh     TKEY_CTRL   C3h   Touch-Key Control Register   x000 0000b     UEP1_DMA_H   EFh Endpoint 1 buffer start address high byte   0000 00xxb     UEP1_DMA_L   EEh_Endpoint 1 buffer start address low byte   xxxx xxxxb     USB related   UEP0_DMA_H   EDh Endpoint 0 and 4 buffer start address high byte   0000 00xxb     registers   UEP0_DMA_L   ECh_Endpoint 0 and 4 buffer start address low byte   xxxx xxxxb     UEP0_DMA_L   ECh_Endpoint 0 and 4 buffer start address low byte   xxxx xxxxb     UEP0_DMA_L   ECh_Endpoint 0 and 4 buffer start address low byte   xxxx xxxxb     UEP0_DMA_L   ECh_Endpoint 0 and 4 buffer start address low byte   xxxx xxxxb     UEP0_DMA   ECh_UEP0_DMA_L and UEP0_DMA_H composed of 16 SFR   0xxxh     UEP2_3_MOD   EBh_Endpoint mode control register 3   0000 0000b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         | ADC_CTRL    | <u>80h</u>     | ADC Control Register                         | <u>x000 0000b</u> |